Die Performance des noch namenlosen RISC-V-Kerns soll 50 Prozent über der des Vorgängers liegen, zudem gibt es die Option für 16-Core-Cluster.

SiFive hat einen neuen Prozessorkern auf Basis der offenen Befehlssatzarchitektur RISC-V vorgestellt, er soll eine 50 Prozent höhere Leistung erreichen als der aktuelle P550. Auf der Linley Fall Processor Conference 2021 erläuterte SiFive das Design des Kerns, der deutlich größere Core-Cluster ermöglicht.

Bei der Ankündigung handelt es sich SiFve zufolge um eine Vorschau, der finale Name und tiefergehende Details sollen erst auf dem RISC-V Summit im Dezember 2021 bekanntgegeben werden. Zumindest eine grobe Performance-Aussage und einige Informationen zum Aufbau hat der US-Hersteller dennoch gegeben.

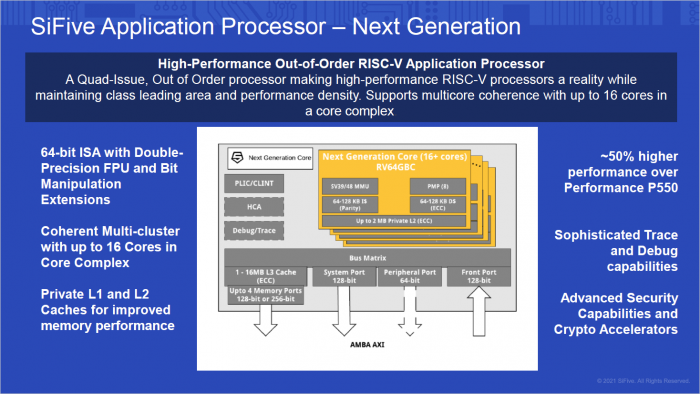

Der 64-Bit-Kern ist wie schon der P550 sogenannter RV64GBC und weist daher eine General-Purpose-, eine Bit-Manipulation- und eine Compressed-Extension auf. SiFive sagt, dass es sich um einen Application Prozessor inklusive MMU für unter anderem Linux handelt, der auch Hypervisor unterstützt. Wie die 50 Prozent höhere Leistung zustande kommt, lässt sich dem simplen Blockdiagramm nur bedingt entnehmen.

Deutlich größere Caches und 16er-Cluster

Allerdings ist zu erkennen, dass das Out-of-Order-Design vierfach statt dreifach breit ausgelegt ist, dass sich der L1-Daten/Instruktionen-Cache jedes Kerns von 32 KByte auf bis zu 128 KByte vervierfacht und dass der L2-Cache bis zu 2 MByte statt 256 KByte fasst. Größere Puffer beschleunigen diverse Applikationen, im Gegenzug fallen aber meist die Latenzen schlechter aus - was einige Programme anteilig verlangsamt.

Abseits der gestiegenen Performance pro Kern lassen sich davon 16 statt 4 zu einem Core-Cluster zusammenschalten. Dieser kann auf bis zu 16 MByte L3-Cache zugreifen, zuvor waren es 4 MByte. Passend dazu hat sich die Anzahl der Memory-Ports vervierfacht, was entsprechend mit einer breiteren Anbindung einher geht.

Insgesamt soll das Design einer der schnellsten und effizientesten RISC-V-Prozessoren sein, die kommerziell verfügbar sind. Aus bei der Metrik der Leistung pro Quadratmillimeter soll der Kern exzellent abschneiden, was wichtig für die Produktionskosten ist.

Offene Befehlssatzarchitektur: SiFive hat den schnellsten RISC-V-Kern - Golem.de - Golem.de

Read More

No comments:

Post a Comment